Projects

Sequel2SQL

Capstone project to improve SQL error correction with an LLM-based workflow for PostgreSQL.

Key Highlights

- Defined the architecture and built an LLM scaffolding that improves SQL error correction through a custom database toolkit, improving baseline performance by 6% on the BIRD-CRITIC benchmark.

E-Commerce Analytics Pipeline

Serverless analytics pipeline for e-commerce events using AWS and Spark.

Key Highlights

- Built a serverless medallion pipeline processing 500K+ e-commerce events on hourly and daily cadences, with pre-aggregated tables for faster downstream analysis.

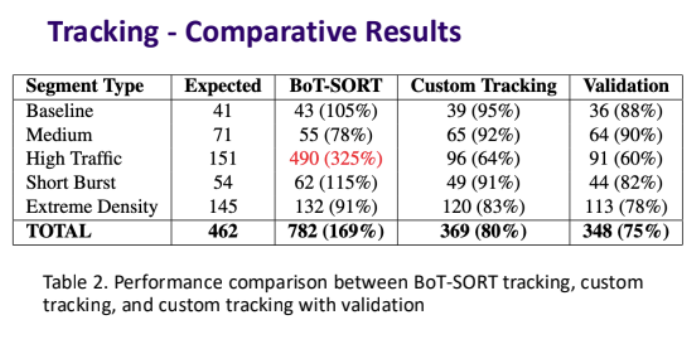

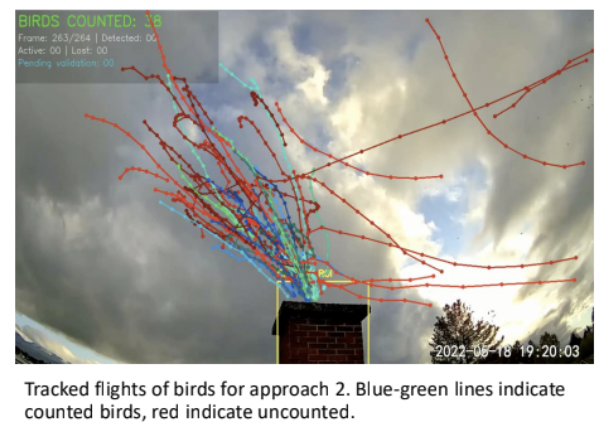

Automated Vaux's Swift Counter

Computer vision pipeline for counting birds in a conservation use case.

Key Highlights

- Built a multi-stage pipeline using YOLOv11, SAM2, and custom trajectory tracking.

- Developed for the Courtenay Museum's Vaux's Swift conservation project.

- Reached over 90% accuracy in low and medium traffic scenarios.

Online Engagement & Review Behavior Study

Statistical study on how business responses are associated with review activity.

Key Highlights

- Analyzed 760K+ Google reviews using matched treatment/control groups and paired t-tests; businesses that responded to reviews were associated with 9 additional reviews on average versus non-responders.

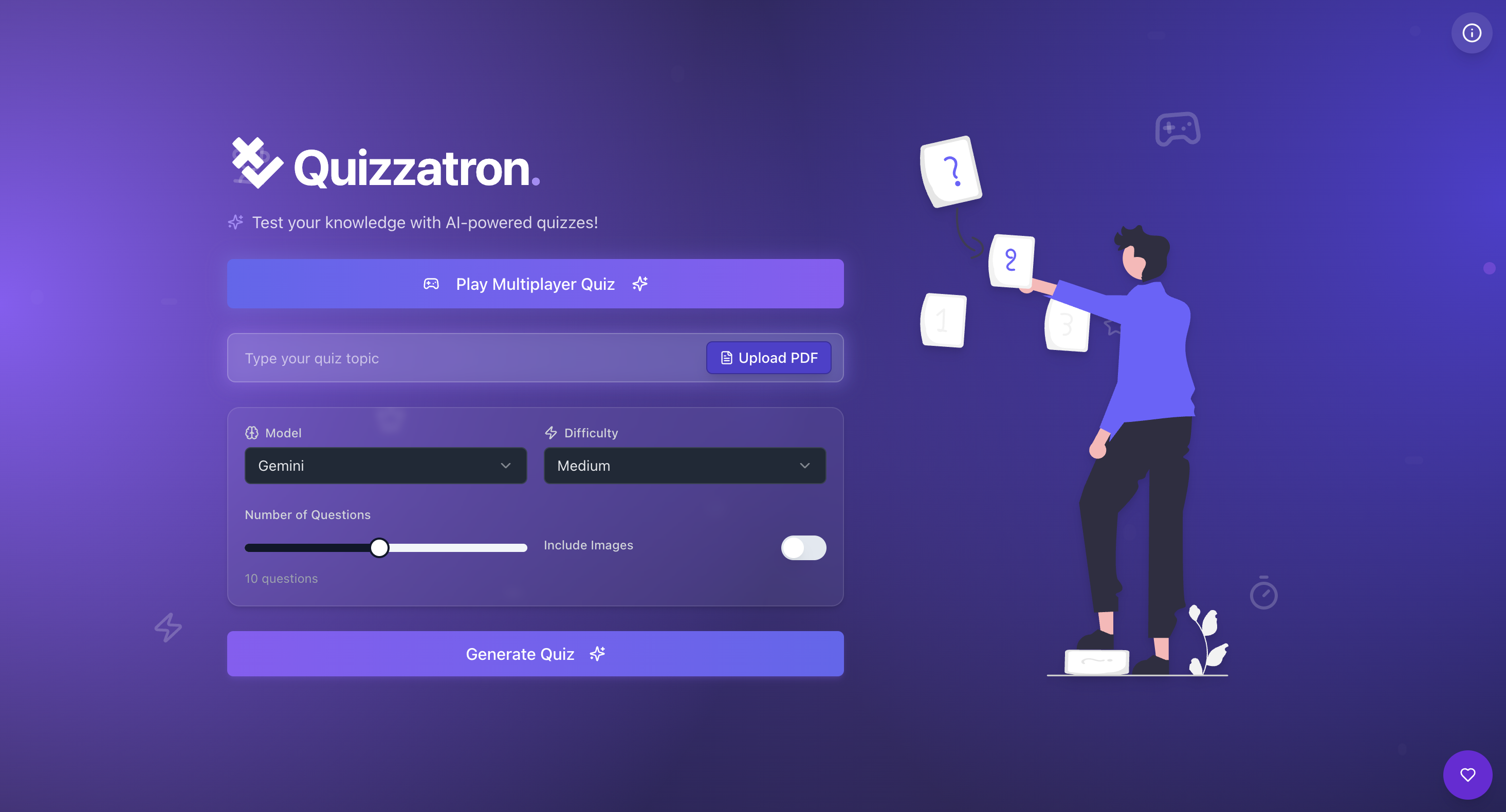

Quizzatron

Web app that generates quizzes from prompts and documents using LLMs.

Key Highlights

- Built a quiz generation app in Streamlit with Google Gemini models.

- Converted prompts and PDFs into interactive quizzes.

- Used by classmates for faster practice-question creation.

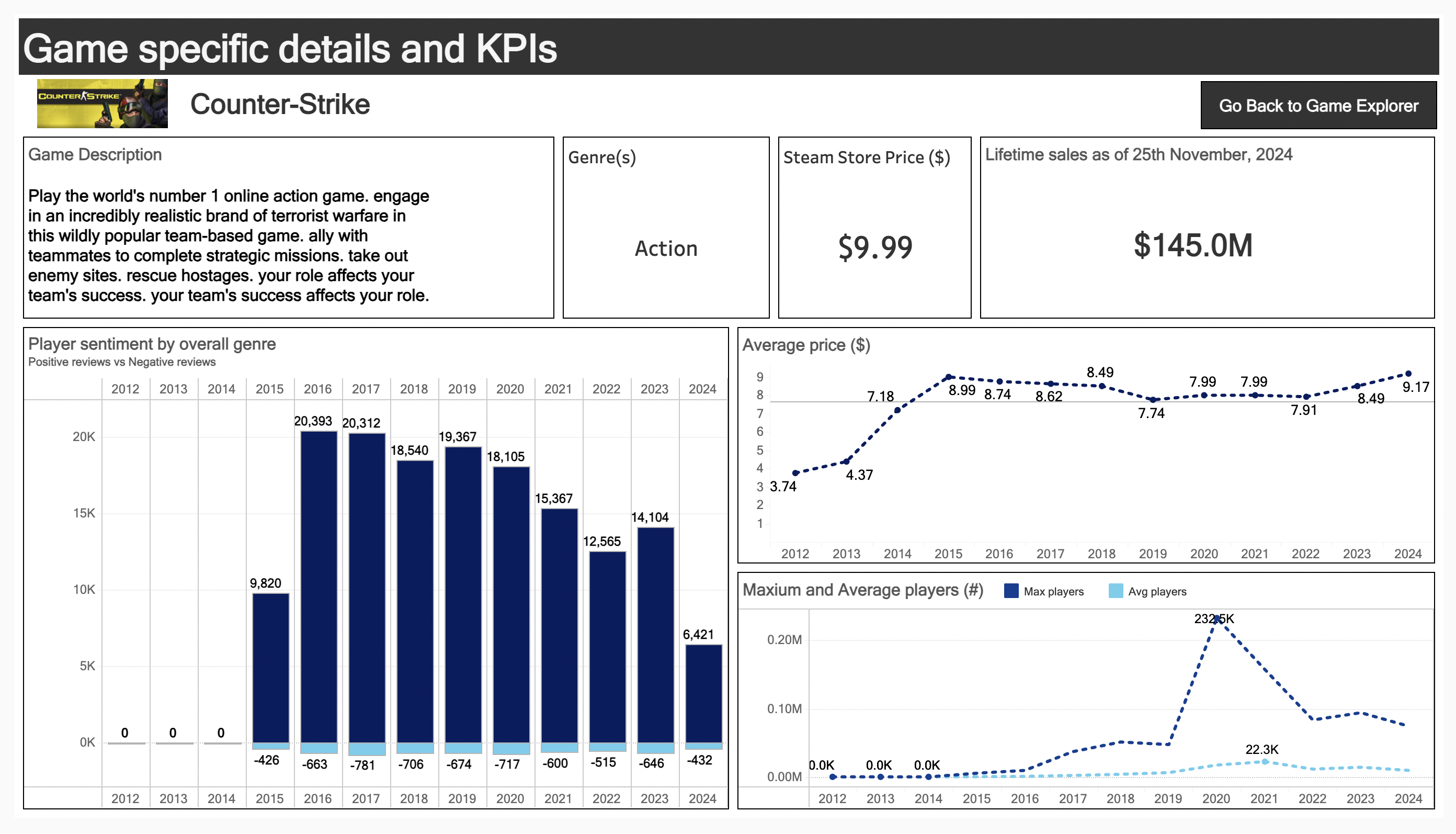

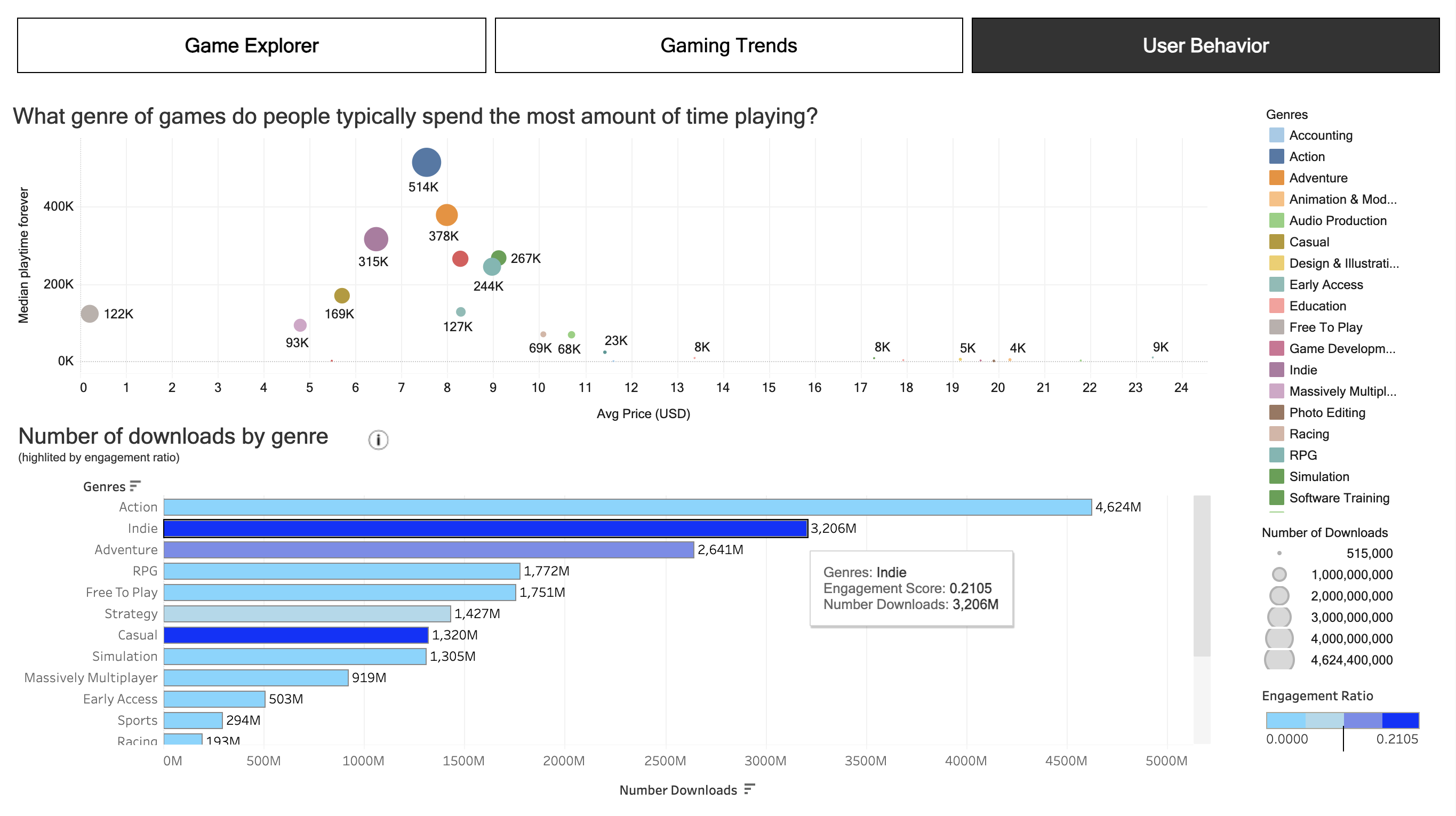

SteamViz

Tableau dashboard exploring Steam game performance and player behavior trends.

Key Highlights

- Built ETL workflows and dashboard views for Steam top-game analysis.

- Compared game performance metrics and player behavior patterns through interactive charts.

AWS CP Creds

Shell utility to update AWS credentials from clipboard text on macOS.

Key Highlights

- Automated updates to ~/.aws/credentials to remove manual edits.

- Added support for multiple profiles with format validation and basic error handling.

- Shared with classmates and used in AWS Academy coursework.

Undergraduate Projects

Hardware and embedded systems projects from undergraduate studies in Electronics & Communication Engineering at PSG College of Technology

ASIC Implementation of AES Cryptographic Algorithm

AES-128/192/256 hardware accelerator for end-to-end encryption in edge devices

Overview

AES-128/192/256 hardware accelerator for end-to-end encryption in edge devices. Makes use of a 32-bit iterative core along with a KeyGen Module. Our team designed the Data Path, Control Path, KeyGen and IO Controller Modules and implemented the same. Successful Encryption/Decryption was achieved on the Basys-3 FPGA with an operating frequency of 100 MHz. Back-end design was done in collaboration with Semi Conductor Laboratory, Chandigarh.

Technical Implementation

- Core Architecture: 32-bit iterative core with KeyGen module for AES-128/192/256

- Module Design: Data Path, Control Path, KeyGen, and IO Controller modules

- FPGA Prototyping: Successfully tested on Basys-3 FPGA at 100 MHz operating frequency

- Back-end Design: Collaborated with Semi Conductor Laboratory, Chandigarh for ASIC back-end flow

Key Contributions

- Designed the Data Path and Control Path modules

- Implemented and verified individual transformation blocks (S-Box, MixColumns, etc.)

- Conducted timing analysis and optimization to meet performance targets

- Developed comprehensive testbenches for functional verification

Key Highlights

- Built AES-128/192/256 hardware accelerator using 32-bit iterative core with KeyGen module

- Achieved successful Encryption/Decryption on Basys-3 FPGA at 100 MHz

- Collaborated with Semi Conductor Laboratory, Chandigarh for ASIC back-end design

- Designed Data Path, Control Path, KeyGen, and IO Controller modules

FPGA Implementation of Elliptic Curve Cryptography Algorithm

Custom processor design with ISA for performing ECC point operations using iterative resource sharing

Overview

Designed and implemented a specialized cryptographic processor for Elliptic Curve Cryptography (ECC). Our team designed the core data path and control path modules for performing ECC operations with an Instruction Set Architecture using iterative resource sharing, similar to a microprocessor. A POC for Homomorphic extension of ECC was also developed.

Architecture Design

- Custom ISA: Designed instruction set to perform Point Addition and Point Doubling operations with iterative resource sharing

- Datapath Design: Implemented arithmetic units for finite field operations (addition, multiplication, inversion)

- Control Path: Designed control logic to orchestrate ECC algorithms

- Homomorphic Extension: Developed proof-of-concept for Homomorphic extension of ECC

Key Contributions

- Designed the core data path and control path modules

- Implemented ISA with iterative resource sharing concept

- Developed POC for Homomorphic extension of ECC

- Verified correctness against standard ECC test vectors

Key Highlights

- Designed ISA for Point Addition and Point Doubling with iterative resource sharing

- Implemented core data path and control path modules for ECC operations

- Developed proof-of-concept for Homomorphic extension of ECC

- Achieved successful encryption/decryption with standard ECC test vectors

Surface Waste Accumulator Bot

Automated floating robot for collecting surface waste from water bodies using embedded systems

Overview

Developed an autonomous floating robot designed to accumulate surface waste from local water bodies, providing a cost-effective solution for environmental conservation. This project combines robotics, embedded systems programming, and environmental engineering.

Problem Statement

Local water bodies face significant pollution from floating debris and surface waste. Manual cleaning is labor-intensive and costly. This project aimed to create an automated, low-cost solution for continuous waste collection.

Technical Implementation

Hardware Design

- Platform: Designed floating platform with stability for water operation

- Collection Mechanism: Implemented mechanical system for waste capture and storage

- Motor Control: DC motors with PWM control for navigation

- Sensors: Ultrasonic and IR sensors for obstacle detection and navigation

Software Architecture

- Movement Algorithm: Designed algorithm for efficient coverage of testing area

- Obstacle Avoidance: Implemented real-time path planning to navigate around obstacles

- State Machine: Developed finite state machine for behavior control

- Power Management: Optimized for extended operation time

Key Contributions

- Played a crucial role in designing the movement algorithm for the testing environment

- Implemented embedded C code for Arduino microcontroller

- Developed sensor fusion for navigation and obstacle detection

- Conducted field testing and iterative improvements

Impact

This project demonstrates practical engineering skills applied to environmental problems, combining hardware design, embedded programming, and algorithm development to create a working prototype for water conservation.

Key Highlights

- Designed movement algorithm for autonomous navigation in water bodies

- Implemented embedded C code for motor control and sensor integration

- Developed obstacle avoidance system using ultrasonic and IR sensors

- Created low-cost solution for environmental waste management

Implementation of CLEFIA Cryptographic Algorithm

Hardware implementation of CLEFIA block cipher focusing on key scheduling and arithmetic blocks

Overview

Implemented hardware modules for the CLEFIA cryptographic algorithm, a block cipher designed for both software and hardware efficiency. This project focused on the Key Scheduling Algorithm (KSA) and critical arithmetic blocks required for the cipher operations.

About CLEFIA

CLEFIA is a 128-bit block cipher supporting key lengths of 128, 192, and 256 bits. Developed by Sony, it's designed for high security and efficiency across various platforms, from embedded devices to high-performance systems.

Technical Implementation

Key Scheduling Algorithm (KSA)

- Main Focus: Implemented complete key expansion logic

- Round Key Generation: Designed hardware to generate round keys from master key

- Optimization: Balanced area and timing for efficient FPGA implementation

Arithmetic Blocks

- S-Boxes: Implemented substitution boxes for non-linear transformation

- Diffusion Functions: Designed arithmetic blocks for data mixing (F-functions)

- XOR Networks: Implemented whitening key operations

Key Contributions

- Mainly worked on implementing the Key Scheduling Algorithm

- Designed and implemented several arithmetic blocks for core cipher operations

- Conducted functional verification and timing analysis

- Integrated modules into complete CLEFIA encryption system

Technical Skills Demonstrated

- Hardware description language (Verilog) proficiency

- Understanding of block cipher design principles

- FPGA synthesis and implementation using Xilinx ISE

- Cryptographic algorithm analysis and implementation

Key Highlights

- Implemented complete Key Scheduling Algorithm for round key generation

- Designed arithmetic blocks including S-Boxes and diffusion functions

- Achieved functional correctness verified against test vectors

- Demonstrated breadth in cryptographic algorithm implementations

Certifications & Achievements

Certifications

-

Cisco Certified Entry Network Technician (CCENT)

Passed with a score of 924/1000. Demonstrates foundational knowledge in networking concepts, including IP addressing, routing, switching, and network troubleshooting.

-

Academic Credit Courses in Computer Architecture

Completed one-credit courses in System Level Verification Techniques and Methodologies, and Multicore Technology. Advanced coursework in hardware verification and parallel computing architectures.

Achievements

Academic

-

State Level Topper in Engineering Entrance Exams

(2016-05)

Rank 92 out of nearly 300,000 candidates with 99.9th percentile. Scored 98.6% overall.

Leadership

-

IEEE SPAC Chairman

(2019-08)

Served as SPAC (Student Professional Awareness Committee) Chairman for IEEE Students Chapter 12951 for the academic year 2019-20. Led technical events, workshops, and student engagement initiatives.

Sports

-

First Prize - State Level Deadlifting Competition

(2017-04)

Won first prize in the 65kg Weight Class at a state-level powerlifting competition organized by the Indian Bodybuilding Federation (IBF). Demonstrates dedication, discipline, and athletic achievement.